CMOS集成電路設計(二) 接口電路詳解

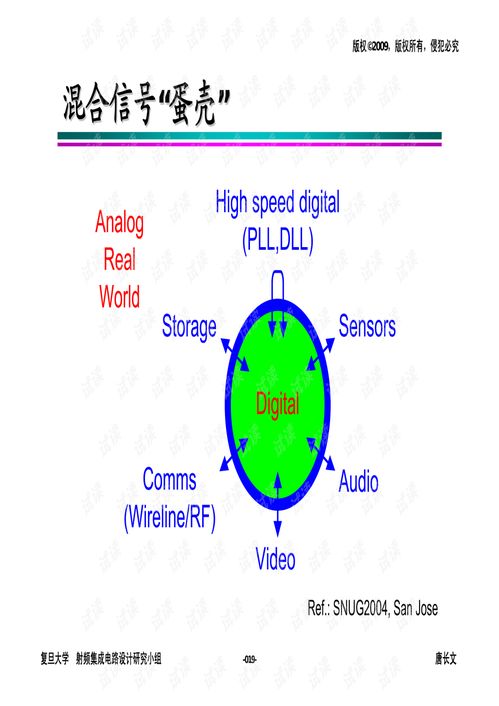

在集成電路(IC)設計中,接口電路扮演著系統內外部或不同模塊間“翻譯官”與“協調員”的關鍵角色。隨著CMOS工藝成為數字與混合信號芯片的主流技術,其接口電路的設計面臨著速度、功耗、噪聲與可靠性等多重挑戰。本文將深入探討CMOS集成電路設計中核心接口電路的原理、類型與設計要點。

一、接口電路的重要性與挑戰

接口電路位于芯片的邊界,負責處理芯片與外部世界(如其他芯片、傳感器、存儲器件或傳輸總線)之間的電信號交互。其主要功能包括:

- 電平轉換:將芯片內部的核心電壓(如1.2V, 0.9V)轉換為與外部標準兼容的電壓(如3.3V LVCMOS, 1.8V HSTL)。

- 驅動能力增強:提供足夠的電流以驅動片外較大的容性負載(如PCB走線、連接器、其他芯片的輸入電容)。

- 噪聲隔離與抗干擾:抑制外部噪聲(如電源噪聲、串擾)對內部敏感核心電路的影響,同時減少芯片開關噪聲對外部的輻射。

- 速度匹配與同步:在高速傳輸中,處理信號時序、建立保持時間,并可能集成時鐘數據恢復(CDR)或鎖相環(PLL)功能。

在納米級CMOS工藝下,設計挑戰尤為突出:核心電壓不斷降低以節省功耗,但I/O電壓可能仍需維持較高水平以兼容舊系統或滿足噪聲容限要求,這增大了電平轉換的設計難度。速度提升導致信號完整性(如反射、振鈴、串擾)和功耗(特別是動態功耗)問題愈發嚴峻。

二、核心接口電路類型詳解

1. 輸入緩沖器(Input Buffer)

輸入緩沖器是外部信號進入芯片的第一道門戶。其基本設計要求是:

- 高輸入阻抗:最小化對前級驅動電路的負載效應。

- 確定的邏輯閾值:能準確識別高、低電平,通常通過一個反相器鏈實現。對于不同標準(如TTL, CMOS),閾值需要調整。

- 抗靜電放電(ESD)保護:集成ESD保護結構(如GGNMOS、二極管鉗位),防止芯片在制造、運輸和使用中被靜電損壞。

- 施密特觸發器輸入:對于緩慢變化或伴有噪聲的輸入信號,采用具有滯回特性的施密特觸發器可以提高噪聲容限,避免誤觸發。

2. 輸出緩沖器(Output Buffer / Driver)

輸出緩沖器負責將內部邏輯信號驅動到片外。其核心是一個按比例放大的反相器鏈( tapered buffer )。設計要點包括:

- 驅動強度選擇:根據負載電容和所需上升/下降時間,計算最終級晶體管的尺寸。驅動能力通常以驅動多大容性負載下的標準上升時間來標定(如50pF @ 5ns)。

- 可控壓擺率:通過控制預驅動級的電流或使用串聯電阻,限制輸出信號的壓擺率(slew rate),以減少高速切換時的電源噪聲和電磁干擾(EMI)。

- 開漏輸出:某些應用(如I2C總線)需要開漏輸出,僅提供下拉路徑,上拉由外部電阻完成,便于實現“線與”功能。

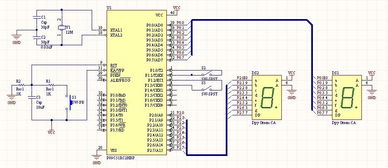

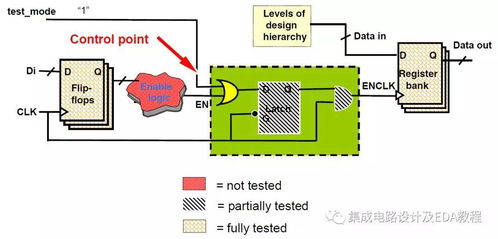

3. 雙向輸入/輸出(Bidirectional I/O)

許多芯片引腳需要復用為輸入或輸出。這通過三態緩沖器實現:

- 結構:包含一個輸出驅動器和一個輸入接收器,由一個使能信號控制方向。當使能有效時,引腳作為輸出;無效時,輸出級處于高阻態,引腳作為輸入。

- 關鍵設計:確保模式切換時無沖突電流(即輸出級關閉與輸入級開啟的時序要配合好),并處理好使能信號路徑的延遲,防止“自沖突”。

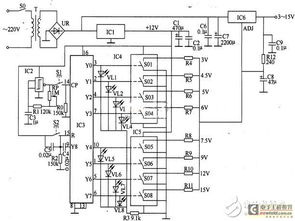

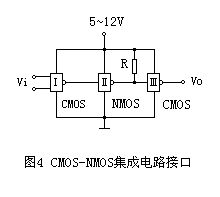

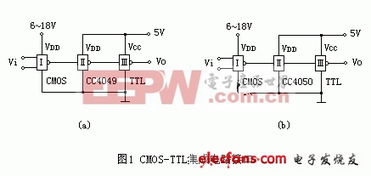

4. 電平轉換器(Level Shifter)

這是連接不同電壓域的核心電路。常見類型有:

- 低到高電平轉換器:將核心低電壓信號(如VDDL=1.0V)轉換到I/O高電壓域(如VDDH=3.3V)。經典結構是交叉耦合的PMOS負載差分對,利用高電壓域電源進行鎖存,確保輸出滿擺幅。

- 高到低電平轉換器:相對簡單,通常一個由高電壓域供電、閾值經過設計的反相器即可實現,但需注意柵氧可靠性(避免高電壓直接加在薄柵氧晶體管上)。

- 雙向電平轉換器:用于雙向總線,結構更為復雜,需要自動感知信號方向并進行相應轉換。

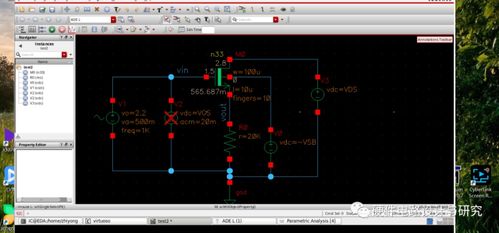

5. 高速接口電路

對于串行接口(如SerDes)、存儲器接口(如DDR)等,接口電路更加復雜:

- 差分信號:使用LVDS(低壓差分信號)、CML(電流模邏輯)等差分I/O,以提高抗共模噪聲能力和速度。

- 阻抗匹配:集成片內終端電阻(如DDR的ODT),并與PCB傳輸線特性阻抗匹配,減少反射。

- 時序調整:集成可編程延遲線、DLL(延遲鎖相環)來精確控制數據與時鐘的相位關系。

- 預加重與均衡:在發送端進行預加重(預失真),在接收端進行均衡(如CTLE),以補償信道的高頻損耗,提高數據率。

三、設計考慮與趨勢

- 電源與地隔離:I/O電路通常使用獨立的電源焊盤和地焊盤(“干凈”的I/O VDD/VSS),并與核心電源/地通過片上或封裝電感進行隔離,以防止“地彈”和“電源噪聲”相互串擾。

- ESD與閂鎖效應防護:除了I/O焊盤本身的ESD結構,整個I/O環與核心區域之間需要布置保護環(Guard Ring)以防止閂鎖效應。

- 先進封裝的影響:隨著Chiplet、2.5D/3D集成技術的發展,接口電路需要適應更短距離、更高密度的互連(如硅通孔TSV、微凸塊),設計重點轉向極低功耗、極高帶寬的近距離接口協議。

- 工藝協同優化:先進工藝節點通常提供多種厚柵氧I/O晶體管選項,專門用于承受更高的I/O電壓,設計時需要合理選擇。

###

接口電路是CMOS集成電路通向物理世界的橋梁,其性能直接影響整個系統的穩定性、速度與兼容性。優秀的設計需要在速度、功耗、面積、魯棒性之間取得精妙平衡,并深入理解工藝特性、封裝模型與系統應用需求。隨著系統復雜度和數據速率持續攀升,接口電路的設計將繼續是集成電路工程中一個充滿挑戰與創新的關鍵領域。

如若轉載,請注明出處:http://m.brq77.cn/product/72.html

更新時間:2026-03-01 10:48:17