模擬CMOS集成電路仿真設(shè)計(jì)基礎(chǔ) 共漏跟隨器及其在集成電路設(shè)計(jì)中的關(guān)鍵作用

在模擬CMOS集成電路設(shè)計(jì)中,共漏跟隨器(Common-Drain Configuration),常被稱為源極跟隨器(Source Follower),是一種基礎(chǔ)而重要的單級(jí)放大器結(jié)構(gòu)。它不僅作為電壓緩沖器,還在信號(hào)鏈中扮演著阻抗變換與電平位移的關(guān)鍵角色。本文將深入探討其基本工作原理、關(guān)鍵特性,并結(jié)合仿真設(shè)計(jì)基礎(chǔ),闡述其在集成電路設(shè)計(jì)中的應(yīng)用。

一、共漏跟隨器基本結(jié)構(gòu)與工作原理

共漏跟隨器采用NMOS或PMOS晶體管實(shí)現(xiàn)。以NMOS為例,其基本結(jié)構(gòu)為:信號(hào)從柵極輸入,從源極輸出,漏極直接連接至電源VDD(或通過一個(gè)電流源/電阻)。因此,輸入與輸出共享漏極節(jié)點(diǎn),故稱“共漏”。其核心功能是提供一個(gè)高輸入阻抗、低輸出阻抗的電壓緩沖。輸出電壓Vout近似等于輸入電壓Vin減去晶體管的柵源電壓VGS,即Vout ≈ Vin - VGS。由于VGS相對(duì)恒定(在特定偏置電流下),輸出電壓能緊密“跟隨”輸入電壓的變化,但存在一個(gè)直流電平偏移。

二、關(guān)鍵特性分析

- 電壓增益:理想情況下,源極跟隨器的電壓增益略小于1,通常為0.8至0.95,具體取決于晶體管的跨導(dǎo)gm和源極看到的負(fù)載阻抗。增益公式為Av ≈ gm Rout / (1 + gm Rout),其中Rout是輸出節(jié)點(diǎn)的等效電阻。

- 輸入與輸出阻抗:高輸入阻抗是其突出優(yōu)點(diǎn),主要由柵極的極高直流阻抗決定,使其易于從前級(jí)高阻抗節(jié)點(diǎn)獲取信號(hào)。輸出阻抗較低,約為1/gm,這使得它能夠驅(qū)動(dòng)重負(fù)載(如低阻抗線路或容性負(fù)載),減少負(fù)載效應(yīng)。

- 頻率響應(yīng):由于輸出節(jié)點(diǎn)通常存在較大容性負(fù)載,其頻率響應(yīng)受輸出極點(diǎn)限制。但因其簡單的結(jié)構(gòu),通常能提供相對(duì)較寬的帶寬。

- 線性度:在合理偏置下,源極跟隨器能提供良好的線性度,但大信號(hào)擺幅可能因VGS變化引入非線性失真。

三、仿真設(shè)計(jì)基礎(chǔ)與實(shí)踐考量

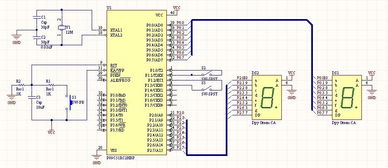

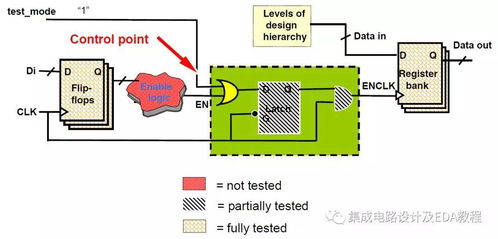

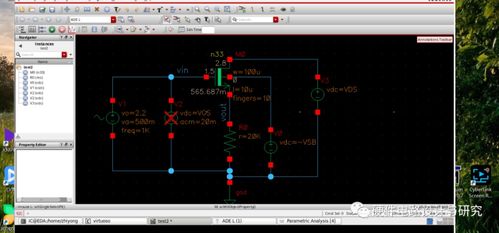

在現(xiàn)代集成電路設(shè)計(jì)流程中,仿真至關(guān)重要。設(shè)計(jì)共漏跟隨器時(shí),需通過仿真軟件(如Cadence Spectre, HSPICE等)進(jìn)行多維度驗(yàn)證:

- 直流工作點(diǎn)仿真:確保晶體管處于飽和區(qū),以獲得穩(wěn)定的VGS和偏置電流。這是電路正常工作的基礎(chǔ)。

- 交流小信號(hào)仿真:測量電壓增益、輸入/輸出阻抗、頻率響應(yīng)(帶寬、相位裕度)等。需注意,仿真應(yīng)包含所有寄生電容和電阻模型,以反映實(shí)際芯片性能。

- 瞬態(tài)仿真:評(píng)估大信號(hào)行為,包括壓擺率、建立時(shí)間、輸出擺幅以及線性度(通過THD分析)。特別要關(guān)注電平位移是否在系統(tǒng)允許范圍內(nèi)。

- 噪聲仿真:分析電路的噪聲貢獻(xiàn),特別是熱噪聲和閃爍噪聲,這對(duì)于高精度模擬系統(tǒng)尤為重要。

- 工藝角與蒙特卡洛分析:考慮工藝偏差、溫度變化對(duì)性能的影響,確保設(shè)計(jì)在各類條件下均穩(wěn)健可靠。

四、在集成電路設(shè)計(jì)中的應(yīng)用

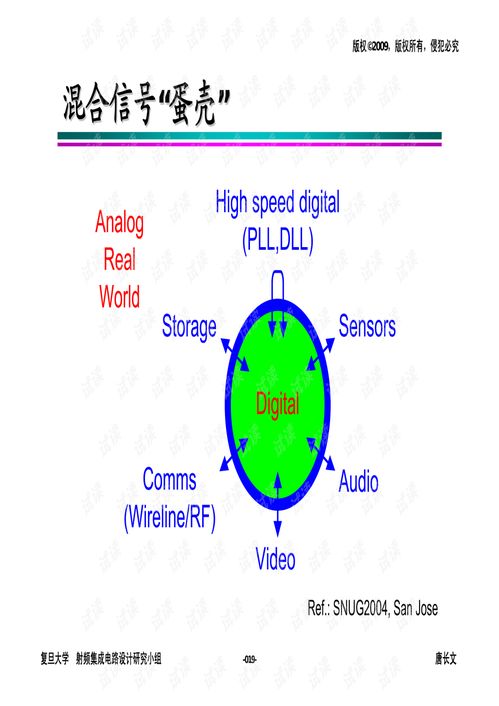

共漏跟隨器廣泛應(yīng)用于各類模擬與混合信號(hào)系統(tǒng)中:

- 電壓緩沖:隔離高阻抗信號(hào)源與低阻抗負(fù)載,防止負(fù)載效應(yīng)導(dǎo)致的信號(hào)衰減。

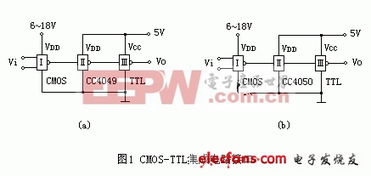

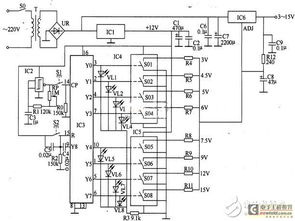

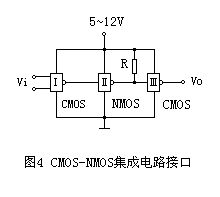

- 電平位移:在不同電壓域之間平移直流電平,例如在低壓核心電路與更高電壓的I/O接口之間。

- 輸出驅(qū)動(dòng):作為最后一級(jí)驅(qū)動(dòng),直接驅(qū)動(dòng)片外負(fù)載或長互連線。

- 參考電壓產(chǎn)生:利用其穩(wěn)定的VGS降,生成一個(gè)比電源電壓低VGS的參考電壓。

設(shè)計(jì)時(shí)需權(quán)衡:增益損失、輸出擺幅限制(受VGS和過驅(qū)動(dòng)電壓影響)、功耗(由偏置電流決定)以及面積(晶體管尺寸和可能的偏置電路)。采用互補(bǔ)結(jié)構(gòu)(如推挽式源極跟隨器)可以改善擺幅和驅(qū)動(dòng)能力。

共漏跟隨器是模擬CMOS設(shè)計(jì)工具箱中的基石。通過深入理解其原理并結(jié)合嚴(yán)謹(jǐn)?shù)姆抡骝?yàn)證,設(shè)計(jì)師能夠有效地將其集成到復(fù)雜系統(tǒng)中,實(shí)現(xiàn)可靠的信號(hào)調(diào)理與接口功能,從而構(gòu)建出高性能、高魯棒性的集成電路。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.brq77.cn/product/66.html

更新時(shí)間:2026-03-01 08:41:13