集成電路設(shè)計入門與技術(shù)要點解析

集成電路設(shè)計是電子工程領(lǐng)域的核心環(huán)節(jié),它決定了芯片的功能、性能和成本。本文將從基礎(chǔ)知識出發(fā),結(jié)合51電子網(wǎng)等技術(shù)資料平臺常見內(nèi)容,梳理集成電路設(shè)計的主要流程與技術(shù)要點。

一、集成電路設(shè)計的基本概念

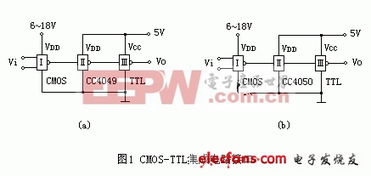

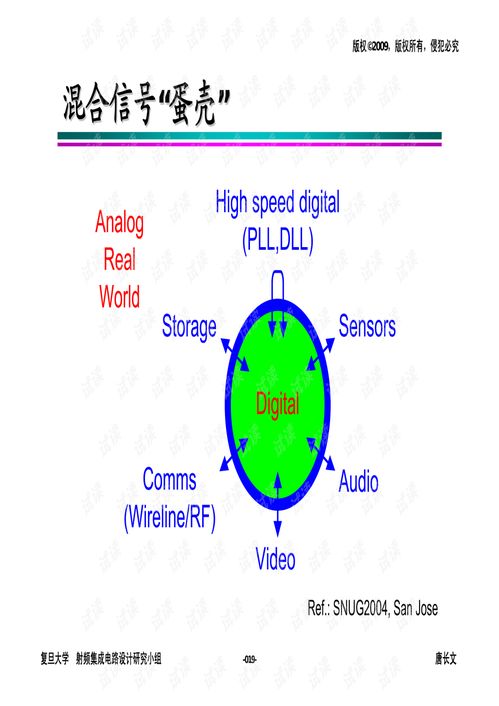

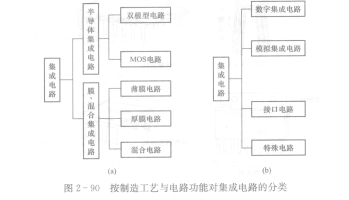

集成電路設(shè)計是指根據(jù)系統(tǒng)需求,利用電子設(shè)計自動化(EDA)工具,在硅片上規(guī)劃并實現(xiàn)晶體管、電阻、電容等元器件互連,以構(gòu)成特定功能電路的過程。其最終目標(biāo)是生成可供芯片制造廠使用的版圖數(shù)據(jù)。設(shè)計層次通常分為系統(tǒng)級、寄存器傳輸級(RTL)、邏輯門級、電路級和物理版圖級。

二、主流設(shè)計流程與方法

現(xiàn)代集成電路設(shè)計主要采用自上而下的設(shè)計方法:

- 規(guī)格定義:明確芯片的功能、性能、功耗、封裝等指標(biāo)。

- 架構(gòu)設(shè)計:進(jìn)行模塊劃分,確定數(shù)據(jù)流與控制流。

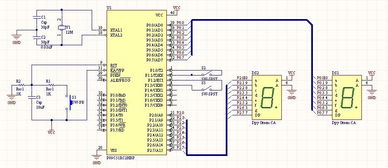

- RTL設(shè)計:使用硬件描述語言(如Verilog或VHDL)編寫代碼,描述電路行為。

- 邏輯綜合:將RTL代碼轉(zhuǎn)換為門級網(wǎng)表,并進(jìn)行邏輯優(yōu)化。

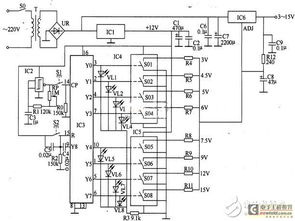

- 物理設(shè)計:包括布局規(guī)劃、單元布局、時鐘樹綜合、布線等步驟,生成最終版圖。

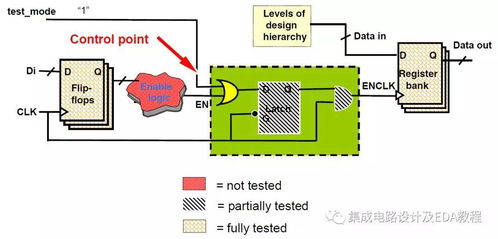

- 驗證與仿真:貫穿整個流程,包括功能驗證、時序驗證、物理驗證等,確保設(shè)計正確性。

三、關(guān)鍵技術(shù)與挑戰(zhàn)

- 低功耗設(shè)計:隨著移動設(shè)備普及,動態(tài)功耗與靜態(tài)漏電功耗的控制成為關(guān)鍵,常用技術(shù)包括電源門控、多閾值電壓、動態(tài)電壓頻率調(diào)節(jié)等。

- 時序收斂:在高頻率設(shè)計中,必須確保信號在時鐘約束下穩(wěn)定傳輸,這涉及精細(xì)的時鐘樹設(shè)計和時序優(yōu)化。

- 可制造性設(shè)計(DFM):考慮工藝波動的影響,通過添加冗余通孔、優(yōu)化線寬等方式提高芯片良率。

- 先進(jìn)工藝挑戰(zhàn):在納米級工藝下,互連線延遲、信號完整性、熱效應(yīng)等問題日益突出,需要更復(fù)雜的建模與仿真。

四、學(xué)習(xí)資源與工具推薦

對于初學(xué)者,可以借助51電子網(wǎng)等平臺提供的技術(shù)資料、數(shù)據(jù)手冊和設(shè)計實例入門。常用的EDA工具包括:

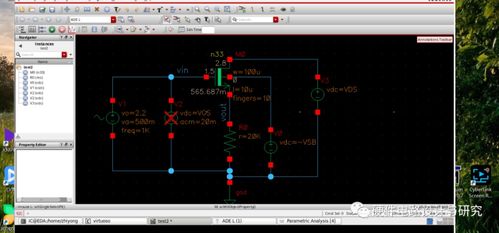

- 設(shè)計輸入:Cadence Virtuoso, Mentor Graphics(現(xiàn)Siemens EDA)系列工具

- 仿真驗證:Synopsys VCS, Cadence Incisive, ModelSim

- 綜合工具:Synopsys Design Compiler

- 物理設(shè)計工具:Cadence Innovus, Synopsys IC Compiler

開源工具如Qflow、Magic、NGSPICE也為學(xué)習(xí)提供了低成本選擇。

集成電路設(shè)計是一門多學(xué)科交叉的工程藝術(shù),需要扎實的半導(dǎo)體物理、電路理論和軟件工具操作能力。隨著人工智能、物聯(lián)網(wǎng)等新興領(lǐng)域的發(fā)展,對高性能、低功耗芯片的需求將持續(xù)推動設(shè)計技術(shù)創(chuàng)新。設(shè)計者應(yīng)保持持續(xù)學(xué)習(xí),關(guān)注業(yè)界動態(tài)與工藝演進(jìn),方能在快速迭代的技術(shù)浪潮中立足。

如若轉(zhuǎn)載,請注明出處:http://m.brq77.cn/product/59.html

更新時間:2026-03-01 14:57:14