集成了ARM Cortex-M0內(nèi)核微處理器的電容式觸摸感應(yīng)芯片的集成電路設(shè)計(jì)

隨著物聯(lián)網(wǎng)、智能家居和便攜式設(shè)備的飛速發(fā)展,對(duì)高性能、低功耗且集成度高的微控制器需求日益增長(zhǎng)。其中,集成了ARM Cortex-M0內(nèi)核的微處理器,因其出色的能效比、精簡(jiǎn)的指令集和成熟的生態(tài)系統(tǒng),已成為嵌入式系統(tǒng)設(shè)計(jì)的理想選擇。當(dāng)此類內(nèi)核與先進(jìn)的電容式觸摸感應(yīng)技術(shù)結(jié)合,形成一顆專用的電容式觸摸感應(yīng)處理器芯片時(shí),便能創(chuàng)造出高度集成、響應(yīng)靈敏且用戶友好的智能交互解決方案。本文將探討這類芯片的集成電路設(shè)計(jì)關(guān)鍵考量。

一、 核心架構(gòu)與系統(tǒng)集成

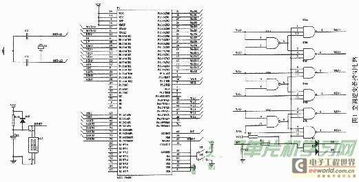

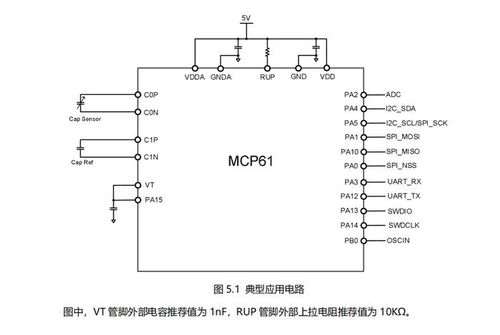

設(shè)計(jì)的核心是ARM Cortex-M0處理器。它是一個(gè)32位精簡(jiǎn)指令集(RISC)內(nèi)核,具有低功耗、小硅片面積和高代碼效率的特點(diǎn)。在芯片設(shè)計(jì)中,Cortex-M0作為主控制器,負(fù)責(zé)執(zhí)行觸摸感應(yīng)算法、處理外部中斷、管理通信接口(如I2C、SPI、UART)以及控制其他外設(shè)。

圍繞該內(nèi)核,需要集成一系列專用和通用功能模塊:

- 電容式觸摸感應(yīng)前端:這是芯片的“感官”部分。通常包括多個(gè)高靈敏度、低噪聲的電容傳感通道(對(duì)應(yīng)多個(gè)觸摸按鍵、滑條或滾輪)。前端電路負(fù)責(zé)將微小的電容變化(由手指觸摸引起)轉(zhuǎn)換為可測(cè)量的電信號(hào)(如電壓或頻率變化)。

- 模擬-數(shù)字轉(zhuǎn)換器:一個(gè)高精度、低功耗的ADC(模數(shù)轉(zhuǎn)換器)至關(guān)重要,用于將模擬傳感信號(hào)數(shù)字化,供Cortex-M0內(nèi)核進(jìn)行算法處理。通常采用逐次逼近型或Σ-Δ型ADC以滿足精度和噪聲抑制要求。

- 數(shù)字信號(hào)處理單元:雖然Cortex-M0可以運(yùn)行軟件算法,但為了進(jìn)一步降低CPU負(fù)載和功耗,有時(shí)會(huì)集成專用的硬件協(xié)處理器或狀態(tài)機(jī),用于執(zhí)行基礎(chǔ)的濾波、基線跟蹤和閾值比較等重復(fù)性任務(wù)。

- 存儲(chǔ)器:集成適量的Flash存儲(chǔ)器(用于存儲(chǔ)固件代碼)和SRAM(用于程序運(yùn)行和數(shù)據(jù)緩存),容量根據(jù)應(yīng)用復(fù)雜度和通道數(shù)量確定。

- 電源管理單元:為實(shí)現(xiàn)低功耗運(yùn)行,尤其是電池供電場(chǎng)景,需要一個(gè)高效的PMU。它應(yīng)支持多種工作模式(如運(yùn)行、睡眠、深度睡眠),并能動(dòng)態(tài)調(diào)節(jié)內(nèi)核、外設(shè)和傳感電路的電壓與時(shí)鐘頻率。

- 時(shí)鐘系統(tǒng)與復(fù)位電路:提供穩(wěn)定的系統(tǒng)時(shí)鐘(可能包括內(nèi)部RC振蕩器和外部晶體振蕩器接口)以及可靠的上下電復(fù)位和看門狗功能。

- 通用輸入輸出與通信接口:提供豐富的GPIO,部分可復(fù)用于觸摸通道;集成標(biāo)準(zhǔn)通信接口,便于與主控MCU或傳感器網(wǎng)絡(luò)連接。

二、 電容傳感關(guān)鍵技術(shù)設(shè)計(jì)

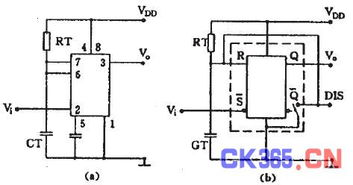

- 傳感方案選擇:常見方案有電荷轉(zhuǎn)移、電容數(shù)字轉(zhuǎn)換和弛張振蕩等。設(shè)計(jì)需權(quán)衡靈敏度、響應(yīng)速度、抗噪聲能力和功耗。例如,CDC方案能提供高分辨率的數(shù)字電容值,但功耗可能較高;而弛張振蕩方案結(jié)構(gòu)簡(jiǎn)單、功耗低,適合對(duì)成本敏感的應(yīng)用。

- 噪聲抑制與抗干擾:電容傳感極易受到電源噪聲、射頻干擾和環(huán)境溫濕度變化的影響。設(shè)計(jì)時(shí)必須考慮:

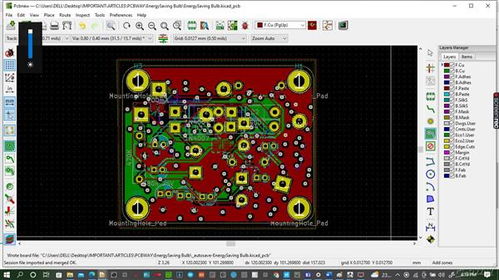

- 硬件層面:采用差分傳感結(jié)構(gòu)、屏蔽驅(qū)動(dòng)技術(shù)、優(yōu)化的PCB布局與走線(在芯片封裝和系統(tǒng)應(yīng)用層面)、內(nèi)部電壓穩(wěn)壓和濾波電路。

- 軟件/算法層面:由Cortex-M0運(yùn)行先進(jìn)的數(shù)字濾波算法(如中值濾波、均值濾波)、自適應(yīng)閾值算法和環(huán)境補(bǔ)償算法,以區(qū)分真實(shí)觸摸和噪聲。

- 靈敏度與功耗平衡:更高的靈敏度意味著能檢測(cè)更輕微或帶手套的觸摸,但通常伴隨著更高的傳感電路功耗和更易受噪聲影響。設(shè)計(jì)需要通過可編程配置(如調(diào)整采樣率、激勵(lì)電流或積分時(shí)間),讓用戶能根據(jù)具體應(yīng)用場(chǎng)景(如家電面板、可穿戴設(shè)備)進(jìn)行優(yōu)化。

三、 低功耗設(shè)計(jì)策略

低功耗是此類芯片的核心競(jìng)爭(zhēng)力之一。策略包括:

- 動(dòng)態(tài)功耗管理:Cortex-M0內(nèi)核本身支持睡眠模式。芯片設(shè)計(jì)應(yīng)允許在無觸摸時(shí),CPU和大部分外設(shè)進(jìn)入休眠,僅由低功耗傳感電路或定時(shí)器周期性喚醒進(jìn)行掃描。

- 模擬電路優(yōu)化:采用亞閾值設(shè)計(jì)技術(shù)、關(guān)斷閑置通道電源、使用開關(guān)電容等低功耗電路結(jié)構(gòu)來構(gòu)建傳感前端和ADC。

- 時(shí)鐘門控與電源門控:在寄存器傳輸級(jí)設(shè)計(jì)時(shí),對(duì)不工作的模塊關(guān)閉時(shí)鐘和電源,顯著降低靜態(tài)和動(dòng)態(tài)功耗。

四、 設(shè)計(jì)流程與驗(yàn)證挑戰(zhàn)

此類芯片設(shè)計(jì)遵循典型的混合信號(hào)IC設(shè)計(jì)流程,但挑戰(zhàn)突出:

- 混合信號(hào)協(xié)同設(shè)計(jì)與仿真:需要精確建模模擬傳感電路、ADC與數(shù)字處理器(Cortex-M0及其外設(shè))之間的交互。使用混合信號(hào)仿真工具確保信號(hào)完整性和系統(tǒng)功能正確。

- IP集成與驗(yàn)證:ARM Cortex-M0是一個(gè)軟核或硬核IP。集成時(shí)需確保其與片上總線(如AHB/APB)、存儲(chǔ)器控制器及自定義外設(shè)的正確連接和時(shí)序收斂。

- 抗靜電與可靠性:作為用戶接口芯片,必須滿足嚴(yán)格的ESD(靜電放電)和EMC(電磁兼容性)標(biāo)準(zhǔn),這需要在芯片I/O設(shè)計(jì)和系統(tǒng)級(jí)防護(hù)上投入大量精力。

- 固件與硬件協(xié)同開發(fā):觸摸性能極大依賴于算法。需要在設(shè)計(jì)早期就開展硬件-軟件協(xié)同驗(yàn)證,使用FPGA原型或仿真模型來開發(fā)和優(yōu)化觸摸感應(yīng)固件庫(kù)。

五、 應(yīng)用與展望

集成了Cortex-M0的電容觸摸處理器芯片,憑借其高集成度、優(yōu)異性能和靈活可編程性,已廣泛應(yīng)用于智能家電控制面板、消費(fèi)電子(手機(jī)、平板配件)、工業(yè)HMI、汽車中控以及智能物聯(lián)網(wǎng)設(shè)備。隨著工藝進(jìn)步和AIoT發(fā)展,此類芯片的設(shè)計(jì)將朝著更高集成度(集成更多傳感器、無線連接)、更強(qiáng)AI處理能力(在邊緣端運(yùn)行更復(fù)雜的觸摸手勢(shì)識(shí)別算法)和超低功耗的方向持續(xù)演進(jìn)。

設(shè)計(jì)一顆成功的集成ARM Cortex-M0的電容式觸摸感應(yīng)芯片,是一個(gè)系統(tǒng)工程,需要在處理器架構(gòu)、模擬混合信號(hào)電路設(shè)計(jì)、低功耗技術(shù)和系統(tǒng)級(jí)應(yīng)用之間取得精妙平衡,最終為用戶帶來無縫、可靠且節(jié)能的觸控體驗(yàn)。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.brq77.cn/product/46.html

更新時(shí)間:2026-03-01 16:01:13