淺談集成電路設(shè)計的物理設(shè)計

集成電路設(shè)計是現(xiàn)代電子技術(shù)的核心領(lǐng)域,涵蓋了從系統(tǒng)架構(gòu)到具體實現(xiàn)的多個環(huán)節(jié)。其中,物理設(shè)計是集成電路設(shè)計流程中至關(guān)重要的一步,它決定了芯片的性能、功耗、面積和可靠性。本文將簡要探討物理設(shè)計的概念、主要任務(wù)及其在集成電路設(shè)計中的重要性。

1. 物理設(shè)計的定義與目標(biāo)

物理設(shè)計,也稱為后端設(shè)計,是將邏輯設(shè)計(如RTL代碼)轉(zhuǎn)化為實際物理布局的過程。其主要目標(biāo)包括:優(yōu)化芯片的時序性能、最小化功耗、減少芯片面積以及確保制造可行性。物理設(shè)計需要綜合考慮電路的速度、功耗和成本,以滿足特定應(yīng)用的需求。

2. 物理設(shè)計的主要任務(wù)

物理設(shè)計通常包括以下幾個關(guān)鍵步驟:

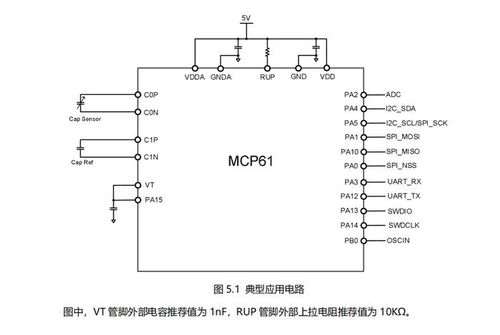

- 布局規(guī)劃:確定芯片上各個功能模塊的位置,優(yōu)化布線資源,減少信號延遲。

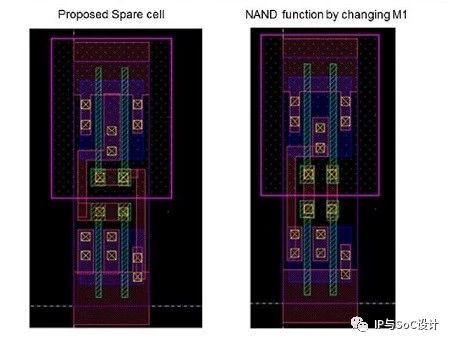

- 布圖:將邏輯單元和宏模塊放置在芯片的適當(dāng)位置,確保空間利用高效。

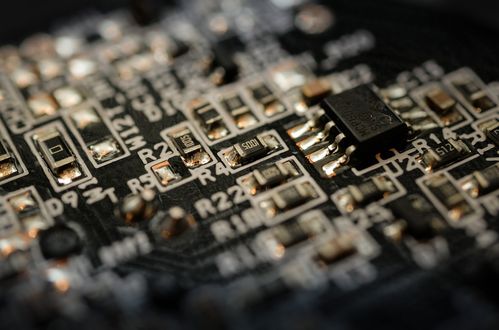

- 布線:連接各個單元和模塊,處理信號路徑,避免電磁干擾和時序問題。

- 時序分析:驗證設(shè)計的時序性能,確保信號在時鐘約束下正確傳輸。

- 功耗和熱分析:評估芯片的功耗分布,進(jìn)行熱管理設(shè)計,防止過熱問題。

- 可制造性設(shè)計:考慮制造工藝的限制,優(yōu)化設(shè)計以提高良率和可靠性。

3. 物理設(shè)計的重要性

物理設(shè)計直接影響芯片的成功與否。一個優(yōu)化的物理設(shè)計可以提升芯片性能,降低功耗,并減少制造成本。例如,在高性能計算和移動設(shè)備中,物理設(shè)計決定了芯片是否能滿足高速運行和低功耗的需求。隨著工藝節(jié)點不斷縮小(如7nm、5nm及以下),物理設(shè)計面臨更多挑戰(zhàn),如寄生效應(yīng)和信號完整性,因此需要先進(jìn)的設(shè)計工具和方法。

4. 結(jié)論

物理設(shè)計是集成電路設(shè)計中不可或缺的環(huán)節(jié),它將抽象的邏輯設(shè)計轉(zhuǎn)化為可制造的物理實體。隨著技術(shù)的發(fā)展,物理設(shè)計將繼續(xù)演進(jìn),以應(yīng)對更復(fù)雜的芯片需求。通過精細(xì)的物理設(shè)計,我們能夠?qū)崿F(xiàn)更高性能、更低功耗的集成電路產(chǎn)品,推動電子行業(yè)的進(jìn)步。

如若轉(zhuǎn)載,請注明出處:http://m.brq77.cn/product/24.html

更新時間:2026-03-01 14:31:27