防護差分功耗分析攻擊的集成電路設計方法

隨著集成電路在安全關鍵領域的廣泛應用,諸如智能卡、加密設備和物聯網節點等,其面臨的安全威脅日益嚴峻。其中,差分功耗分析(DPA)攻擊作為一種非侵入式側信道攻擊手段,通過分析設備運行時的功耗變化來推斷密鑰信息,已成為集成電路安全的主要挑戰之一。因此,開發有效的DPA防護方法在集成電路設計中至關重要。本文將介紹幾種主要的DPA攻擊防護設計方法,包括掩碼技術、隨機化策略、功耗均衡技術以及設計流程中的安全考量,以幫助設計者構建更安全的芯片。

掩碼技術是防護DPA攻擊的經典方法之一。其核心思想是通過引入隨機數據(即掩碼)來混淆敏感操作,使得功耗與密鑰之間的相關性被削弱。例如,在加密算法中,可以對中間值應用隨機掩碼,使得攻擊者無法直接從功耗軌跡中提取有效信息。掩碼技術可分為線性掩碼和非線性掩碼,適用于不同算法結構。掩碼技術可能增加設計復雜度和功耗開銷,因此需在安全性和性能之間進行權衡。

隨機化策略通過引入隨機延遲或隨機操作順序來干擾攻擊者的數據采集。在DPA攻擊中,攻擊者通常需要多次重復測量以平均噪聲,而隨機化可以破壞這種同步性,使得功耗模式難以被分析。例如,在時鐘管理中采用隨機插入空閑周期,或在數據處理中隨機打亂操作序列。這種方法實現相對簡單,但需注意隨機性質量,否則可能被高級攻擊手段繞過。

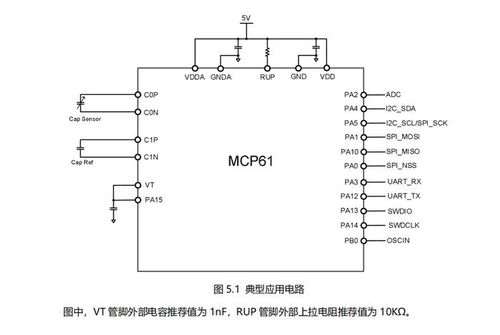

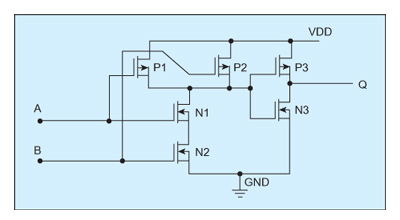

第三,功耗均衡技術旨在使電路的功耗在不同操作下保持一致,從而消除與數據相關的功耗差異。常見的實現包括使用差分邏輯(如WDDL)或電流平衡電路。差分邏輯通過對稱結構確保每個邏輯門在0和1狀態下的功耗相似,而電流平衡電路則通過補償機制穩定整體功耗。盡管功耗均衡技術能有效降低DPA風險,但它可能導致面積和功耗的增加,設計時需進行優化。

在集成電路設計流程中融入安全考量也是關鍵環節。從架構設計到物理實現,每個階段都應評估DPA脆弱性。例如,在RTL設計時采用安全編碼風格,避免使用易受攻擊的結構;在布局布線階段,注意電源分布和信號屏蔽以減少側信道泄漏。同時,結合形式化驗證和仿真測試,可以早期發現潛在漏洞。工具支持,如自動安全分析EDA工具,也正成為行業趨勢。

防護DPA攻擊需要多層次的設計方法。掩碼技術、隨機化策略和功耗均衡技術是核心手段,而全流程的安全意識則確保整體魯棒性。未來,隨著人工智能和機器學習在攻擊中的興起,集成電路設計者需持續創新,結合硬件安全模塊和動態防護機制,以應對不斷演變的威脅。通過綜合應用這些方法,我們可以開發出既高效又安全的集成電路產品,為數字世界提供可靠保障。

如若轉載,請注明出處:http://m.brq77.cn/product/22.html

更新時間:2026-03-01 21:27:20